S

386+ SHRD Логический сдвиг вправо с двойной точностью

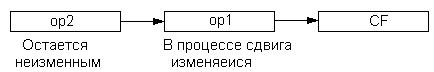

Трехоперандная команда shrd с операндами op1, ор2 и орЗ осуществляет сдвиг вправо первого из своих операндов opl. Число битов сдвига определяется третьим операндом орЗ. По мере сдвига операнда opl вправо выдвигаемые из него младшие биты, пройдя через флаг CF, теряются, а на освобождающиеся места со стороны его старших битов поступают младшие биты второго операнда ор2, как если бы он вдвигался своим правым (младшим) концом в opl. Однако после завершения сдвига значение операнда ор2 не изменяется (рис. П12). Во флаге CF остается последний выдвинутый из операнда opl бит. Максимальное число битов сдвига составляет 31.

В качестве первого операнда opl можно указывать 16- или 32-разрядный регистр общего назначения или 16- или 32-битовую ячейку памяти. Вторым операндом ор2 может служить только 16- или 32-разрядный регистр общего назначения.

Рис. П12. Действие команды shrd.

Третий операнд, характеризующий число битов сдвига, может находиться в регистре CL или быть непосредственным значением.

Команда воздействует на флаги OF, SF, ZF, PF и CF.

Пример 1:

mov AX,0C001h mov BX,900Eh shrd AX,BX,1; AX=6000h, BX=900Eh, CF=1

Пример 2:

mov AX,0C001h mov BX,900Eh shrd AX,BX,2; AX=B000h, BX=900Eh, CF=0

Пример 3:

mov AX,0C001h mov BX,900Eh shrd AX,BX,3; AX=D800h, BX=900Eh, CF=0

Пример 4:

mov EBX,0FFCS000h mov ESI,12345678h mov CL,16 shrd EBX,ESI,CL; EBX=5678FFC8h, ;ESI=12345678h, CF=0

386P+ SIDT Сохранение в памяти содержимого регистра таблицы дескрипторов прерываний

Команда копирует содержимое регистра таблицы дескрипторов прерываний IDTR (линейный базовый адрес таблицы и ее границу) в поле из 6 байт, указанное в качестве операнда.

386Р+ SLDT Сохранение содержимого регистра таблицы локальных дескрипторов

Команда копирует содержимое регистра таблицы локальных дескрипторов LDTR (селектор таблицы) в 16 – или 32-разрядный регистр или в 16- или 32-битовое поле памяти, указанные в качестве операнда.

386Р+ SMSW Сохранение слова состояния машины

Команда smsw считывает слово состояния машины (так называется младшая половина управляющего регистра процессора CRO) и загружает его в указанный в команде 16-разрядный регистр общего назначения или 16-битовое поле памяти.

Команду srnsw можно использовать для перевода процессора из реального в защищенный режим или наоборот. В первом случае после чтения слова состояния командой smsw надо установить в нем бит 0 (бит РЕ) и загрузить назад в CRO командой Imsw. Во втором случае после после чтения слова состояния командой smsw надо сбросить в нем бит 0 и загрузить назад в CRO командой Imsw.