V, X

386Р+ VERR Проверка сегмента на чтение

Команда verr позволяет определить, разрешено ли чтение из сегмента, за которым закреплен селектор, передаваемый команде в качестве ее операнда. Операндом может служить 16-разрядный регистр общего назначения или 16-битовая ячейка памяти.

386Р+ VERW Проверка сегмента на запись

Команда verw позволяет определить, разрешена ли запись в сегмент, за которым закреплен селектор, передаваемый команде в качестве ее операнда. Операндом может служить 16-разрядный регистр общего назначения или 16-битовая ячейка памяти.

486+ XADD Обмен и сложение

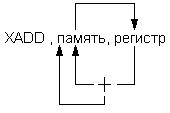

Команда xadd выполняет в одной операции сложение и обмен операндов. Команда требует двух операндов, причем первый операнд должен быть ячейкой памяти, а второй – регистром. После сложения операндов исходное содержимое памяти переносится во второй операнд (регистр), а полученная сумма записывается в память (на место первого слагаемого) (рис. П13). Команда воздействует на флаги OF, SF, ZF, AF, PF и CF.

Рис. П13. Действие команды xadd.

Пример:

; В полях данных mem dw 99 ;В программном сегменте mov AX,48 xadd mem,AX; mem=147, AX=99

XCHG Обмен данными между операндами

Команда xchg пересылает значение первого операнда во второй, а второго – в первый. В качестве любого операнда можно указывать регистр (кроме сегментного) или ячейку памяти, однако не допускается определять оба операнда одновременно как ячейки памяти. Операнды могут быть байтами или словами и представлять числа со знаком или без знака. Команда не воздействует на флаги процессора.

Пример 1:

mov AX,OFF01h mov SI,1000h xchg AX,SI; AX=01000h, SI=FF01h

Пример 2:

;В полях данных: mem dw 0F0F0h ;В программном сегменте mov CX,1256h xchg CX,mem; CX=F0F0h, mem=1256h

Пример 3:

mov AX,6031h xchg AH,AL; AX=3160h

Допустимо использование 32-битовых операндов и дополнительных режимов адресации 32-разрядных процессоров.

Допустимо использование 32-битовых операндов и дополнительных режимов адресации 32-разрядных процессоров.

Пример:

xchg ESI,EDI; ESI и EDI обмениваются содержимым